FIFO

Problem Statement: Design and simulate behavioral model of a FIFO.

What is FIFO?

FIFO is similar to a supermarket checkout line, where the first person in line is served first.

Implementing a behavioral model of FIFO

- Some important points to note

- Two input signals

pushandpopare used to insert and delete data from the data structure. While assertingpush, we must also provide some data to insert in the FIFO. - Two pointers,

Rptr(for read) andWptr(for write) will be used to maintain the FIFO.Rptris incremented upon a read, and theWptris incremented upon a write. - Two flags,

fullandemptycan be used to check and display the status of the FIFO.- While

full = 1, no data shall be inserted in the FIFO, even if provided with thepushsignal. - Similarly, while

empty = 1, no data shall be deleted and/or output should not change, even ifpopsignal tries to delete.

- While

- Two input signals

-

Create a new Verilog file named

fifo.v, and copy-paste the below design. -

Create a new Verilog file and type the below testbench code provided below. Save the file with the same name as the module name.

-

Compile the code and check for any syntax errors using the below command.

iverilog fifo.v tb_fifo.v -o fifo -

If there are no errors, use the below command for running the simulation.

vvp fifoYou will see the values of signals being monitored across each clocktick.

-

If all looks well, use the below command for viewing the waveform. Add the signals from

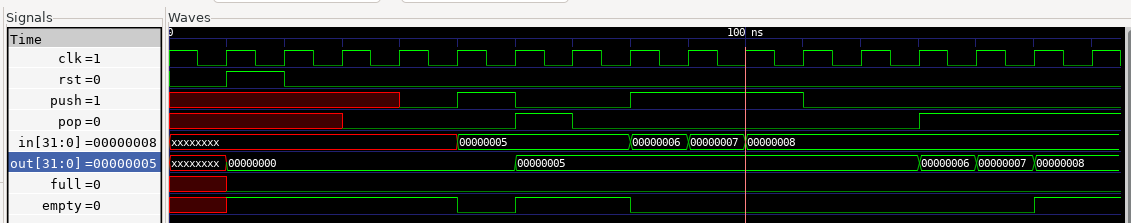

tb_fifodesign to the window to view the simulation output as shown in below image.gtkwave fifo.vcd

- At time, t = 100 ns,

push = 1andin = 32'h00000008, the data is being saved in the FIFO and thus it is neitherfullnorempty. - Eventually when the

pop = 1, the data stored in FIFO is available at theoutport, one at a time. - And as soon as the last data is popped out, the FIFO becomes empty, thus

empty = 1.

- At time, t = 100 ns,